Frequency Divider & Counters

Frequency Divider

A frequency divider can be constructed from J-K flip-flops by taking the output of one cell to the clock input of the next. The J and K inputs of each flip-flop are set to 1 to produce a toggle at each cycle of the clock input. For each two toggles of the first cell, a toggle is produced in the second cell, so its output is at half the frequency of the first. The output of the fourth cell is 1/16 the clock frequency. The same device is useful as a binary counter.

Simulation of Frequency Divider

Counters

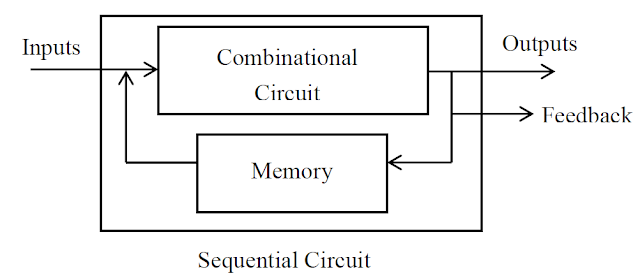

A counting circuit composed of memory elements, such as flip-flops and electronic gates, is the simplest form of sequential circuit available. All sequential circuits are of two types,

- synchronous (clock driven)

- asynchronous (event driven)

In synchronous circuits, changes in the circuit state are synchronised to the normally periodic clock pulses, whereas in event driven circuits state changes are governed by events such as, for example, the occurrence of a system fault.

Binary Counting

A binary counter can be constructed from J-K flip-flops by taking the output of one cell to the clock input of the next. The J and K inputs of each flip-flop are set to 1 to produce a toggle at each cycle of the clock input. For each two toggles of the first cell, a toggle is produced in the second cell, and so on down to the fourth cell. This produces a binary number equal to the number of cycles of the input clock signal. This device is sometimes called a "ripple through" counter. The same device is useful as a frequency divider.

BCD or Decade Counter

A BCD counter or decade counter can be constructed from a straight binary counter by terminating the "ripple-through" counting when the count reaches decimal 9 (binary 1001). Since the next toggle would produce 1010, that drives both X1 and X3 high, and since they are the inputs to the NAND gate, the output of the NAND goes low. This zero output to the asynchronous clear line will clear the registers and start the count over after 9.Simulation for BCD or Decade Counter

Frequency Counter

A frequency counter can be made from a binary counter and a decoder/display unit. In the schematic below an AND gate is used as an input device. The unknown frequency is applied to one input of the AND and sample pulses of precise time interval are applied to the other. When the sample pulse is high, the input signal is transferred to the counter. The number of counts divided by the sample time interval gives the frequency. In the design shown, there is another practical element: after the count is done, there must be time to view the result on the display, so a third input to the AND gate is taken from a J-K flip-flop. The input reaches the counter only when both the sample pulse and the J-K flip-flop are high (counts are collected on alternate sample pulses). This provides an interval when the frequency is displayed. On each positive-going edge of the J-K, a one-shot multivibrator is triggered to send a pulse for resetting the counter.

Comments

Post a Comment